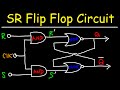

SR Flip-Flop and Logic Gates

Interactive Video

•

Science, Computers

•

9th - 12th Grade

•

Practice Problem

•

Hard

Liam Anderson

FREE Resource

Read more

10 questions

Show all answers

1.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

What is the main difference between an SR latch and an SR flip-flop circuit?

The SR latch uses XOR gates.

The SR flip-flop uses NAND gates.

The SR latch has additional NOR gates.

The SR flip-flop has additional AND gates.

2.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

Which logic gate requires both inputs to be inactive to produce an output of one?

NOR gate

XOR gate

OR gate

AND gate

3.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

What happens to the output of the SR flip-flop when the clock input is zero?

The output becomes one.

The output becomes zero.

The output remains unchanged.

The output changes based on S and R inputs.

4.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

In the SR flip-flop circuit, what is the result when both S and R are zero with an active clock?

Q becomes one and Q bar becomes zero.

Q remains unchanged.

Q becomes zero and Q bar becomes one.

Q and Q bar both become zero.

5.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

What is the state of Q and Q bar when the set button is activated with an active clock signal?

Both Q and Q bar are one.

Both Q and Q bar are zero.

Q is one and Q bar is zero.

Q is zero and Q bar is one.

6.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

What happens when both the set and reset buttons are pressed simultaneously with an active clock?

Q becomes zero and Q bar becomes one.

Q becomes one and Q bar becomes zero.

Q and Q bar both become zero.

Q and Q bar both become one.

7.

MULTIPLE CHOICE QUESTION

30 sec • 1 pt

Why is the condition where both Q and Q bar are zero considered invalid?

Because Q should always be one.

Because both should be one.

Because Q and Q bar should not be equal.

Because Q bar should always be zero.

Access all questions and much more by creating a free account

Create resources

Host any resource

Get auto-graded reports

Continue with Google

Continue with Email

Continue with Classlink

Continue with Clever

or continue with

Microsoft

%20(1).png)

Apple

Others

Already have an account?